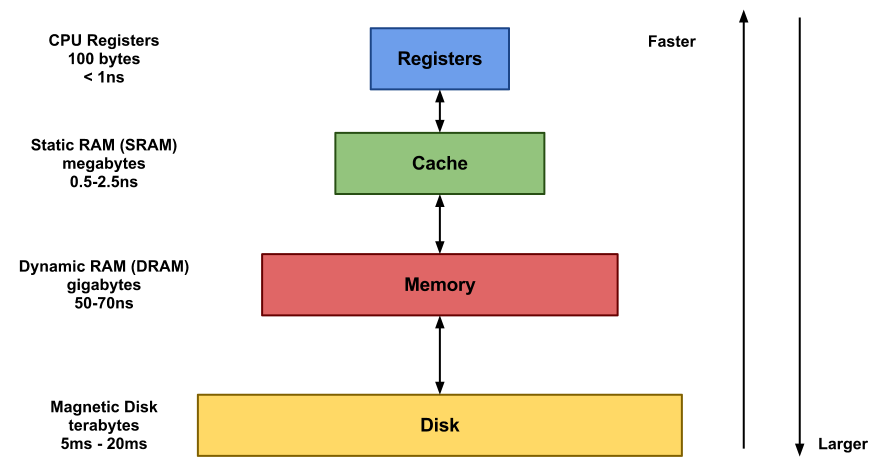

속도가 빠른 장치와 느린 장치에서 속도 차이에 따른 병목 현상을 줄이기 위한 메모리를 말한다.

- 레지스터, 메인 메모리와 함께 메모리 계층 구조의 핵심 계층 중 하나이다.

- 데이터 지역성을 활용하여 메인 메모리에 있는 데이터를 캐시 메모리에 불러와 두고, 프로세서가 필요한 데이터를 캐시 메모리에서 먼저 찾도록 하면 시스템 성능을 향상 시킬 수 있다.

- CPU에서는 이러한 캐시 메모리가 2~3개 정도 사용된다(L1, L2, L3 캐시 메모리),

- 속도, 크기에 따라 분류한 것으로, 일반적으로 L1 캐시부터 먼저 사용된다.

작동 원리

for (i = 0; i < 10; i += 1){

arr[i] = i;

}시간 지역성

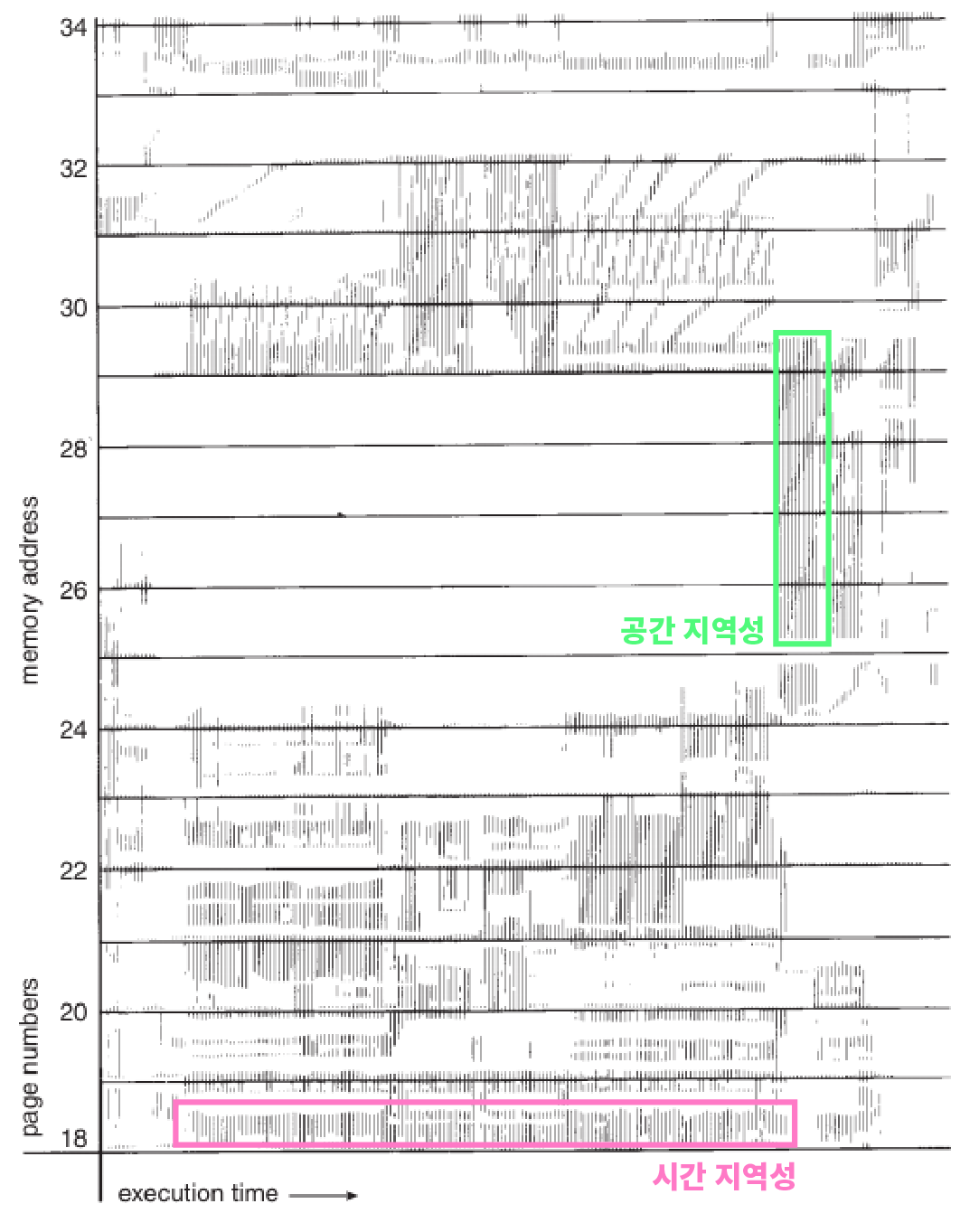

- 최근 접근한 데이터에 다시 접근하는 경향

- 루프에서 인덱스 역할을 하는 변수 i

공간 지역성

- 최근 접근한 데이터의 주변 공간에 다시 접근하는 경향

- 배열 arr의 각 요소를 참조하면서 가까운 메모리 공간에 연속적 접근할 때(arr[1], arr[2]….)

- 가로 축은 실행 시간, 세로 축은 메모리 주소 일 때, 가로로 쭉 늘어진 기록은 긴 시간에 걸려 같은 메모리 주소를 참조한 것이므로 시간 지역성, 세로로 쭉 늘어진 기록은 같은 시간에 인접한 메모리 주소를 참고한 것이므로 공간 지역성이다.

캐시 구조 및 작동 방식

- Direct Mapped Cache

- 가장 기본적인 구조로, DRAM의 여러 주소가 캐시 메모리의 한 주소에 대응되는 다대일 방식

- 현재 그림에서는 메모리 공간이 32개(00000~11111)이고, 캐시 메모리 공간은 8개(000~111)인 상황 ex) 00000, 01000, 10000, 11000인 메모리 주소는 000 캐시 메모리 주소에 맵핑

- 이때 000이 '인덱스 필드', 인덱스 제외한 앞의 나머지(00, 01, 10, 11)를 '태그 필드'라고 한다.

- 이처럼 캐시메모리는

인덱스 필드 + 태그 필드 + 데이터 필드로 구성된다.

- 간단하고 빠른 장점이 있지만, Conflict Miss가 발생하는 것이 단점이다. 위 사진처럼 같은 색깔의 데이터를 동시에 사용해야 할 때 발생한다.

- Fully Associative Cache

- 비어있는 캐시 메모리가 있으면, 마음대로 주소를 저장하는 방식

- 저장할 때는 매우 간단하지만, 찾을 때가 문제

- 조건이나 규칙이 없어서 특정 캐시 Set 안에 있는 모든 블럭을 한번에 찾아 원하는 데이터가 있는지 검색해야 한다. CAM이라는 특수한 메모리 구조를 사용해야하지만 가격이 매우 비싸다.

- Set Associative Cache

- Direct + Fully 방식이다. 특정 행을 지정하고, 그 행안의 어떤 열이든 비어있을 때 저장하는 방식이다. Direct에 비해 검색 속도는 느리지만, 저장이 빠르고 Fully에 비해 저장이 느린 대신 검색이 빠른 중간형이다.

캐시 성능 측정

- Hit latency, Miss latency가 두 요인이다.

- CPU에서 요청한 데이터가 캐시에 존재하는 경우 캐시 히트라고 한다.

- Hit latency

- hit가 발생해 캐싱된 데이터를 가져올 때 소요되는 시간

- Miss latency

- miss가 발생해 상위캐시에서 데이터를 가져오거나 메모리에서 데이터를 가져올 때 소요되는 시간

- 평균 접근 시간(Average access time)

- Miss rate = Cache misses / Cache accesses

- Average access time = Hit latency + Miss rate x Miss latency

캐시 미스가 날 경우

- Cold miss

- 해당 메모리 주소를 처음 불러서 나는 미스

- Conflict miss

- 캐시 메모리에 A와 B 데이터를 저장해야 하는데, A와 B가 같은 캐시 메모리 주소에 할당되어 있어서 나는 미스 (direct mapped cache에서 많이 발생)

- Capacity miss

- 캐시 메모리의 공간이 부족해서 나는 미스 (Conflict는 주소 할당 문제, Capacity는 공간 문제)

캐시 미스 해결 방법

- 캐시 사이즈 늘리기

- 캐시 사이즈를 늘림으로써 capacity miss를 줄일 수 있다.

- 높은 연관 캐시

- Way가 높아질수록 conflict miss를 줄일 수 있다.

- Pseudo - associative cache

- conflict miss는 줄일 수 있지만 , capacity miss가 증가할 수 있다. 기본적으로 2-way associative cache와 비슷하다

- 키 아이디어: 하나의 index를 두 번 비교한다.

- 기본구조

- Cache 내부는 H1과 H2로 나누어져 있다. (논리적인 분할, 실제 분할이 아님)

- 동작원리

- 임의의 index에 대하여 H1를 체크한 뒤, miss가 나면 H2를 체크한다.

- H1을 체크할 땐 regular index를 이용하여 체크하고 H2를 체크할 때는 hashing한 index를 가지고 체크한다.

- H2에 속해있는 set를 표시하기 위해 hashing bit가 필요하다.

- Hit or Miss 처리

- H1 miss/ H2 hit시, 서로의 cache line을 swap

- H1 miss/ H2 miss시, memory data를 가져와서 H1의 cache line으로 올린다.

- 기본구조

- 이렇듯, 하나의 index를 두 번 비교하며 H1과 H2를 sequential하게 체크하므로 hit time이 약간 늘어난다. 하지만 conflict cache miss가 줄어든다.

출처 :

https://gyoogle.dev/blog/computer-science/computer-architecture/캐시 메모리.html